The design of the linear PSU of the computer within the limits of the project cMP2.

The primary goal at replacement of a computer power supply unit by linear one was elimination of impulse hindrances of the power supply unit and minimization of interferences of separate chains of the computer against each other. In particular it is very important to allocate a power supply unit for a sound card in the particular (first) module, i.e. supply it not only from the particular regulator, but also from the particular transformer. Also it is considered that the CPU is a source of strong impulse noise. We also allocate its power supply unit in the particular (second) module. The third module is most loaded, provides a supply for socket P24 of a system board. And the fourth module is the service module. The power supply sockets of the hard disk, the monitor which has been built in the case of the computer, usb devices etc are connected to it. The quantity of supply voltages in this module (and output currents) are defined by a concrete configuration of the computer (type of the used equipment, power consumption).

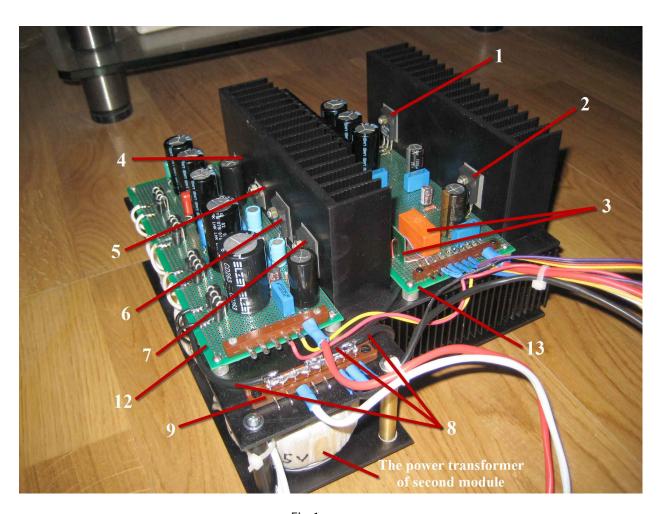

Fig.1

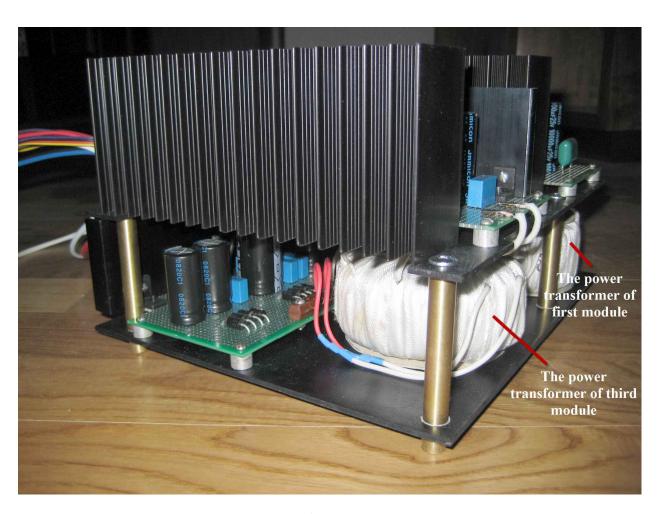

Fig.2

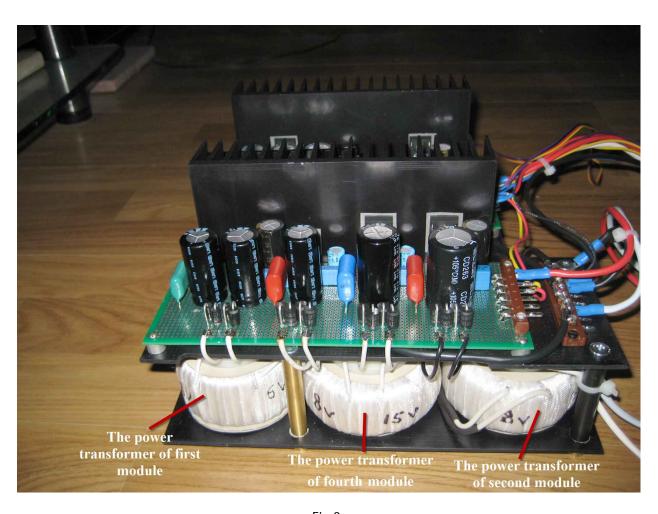

Fig.3

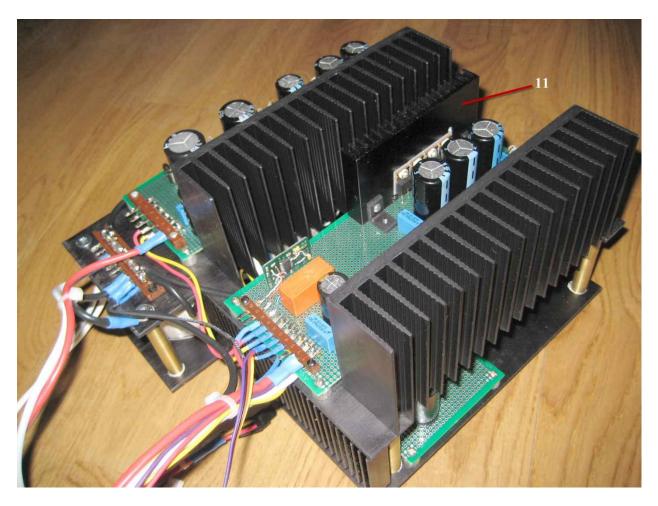

Fig.4

First module. It is on the circuit board (position 12 in the fig. 1).

The first module is defined for a supply of a digital part of sound card Esi@Juli (the analogue part is not used) and provides the stabilized voltage + 5 V (see Appendix 2). The digital part of sound card Esi@Juli consumes the maximum current 170 MA (in a play mode). The first module should provide not less double current consumption. The maximum output current of this module is 2 A. The power transformer is toroidal 60 VA; the voltage of a secondary winding in an idling mode is 6-8 V. The Schottky rectifiers with maximum average forward rectified current 3-5 A (SR350, SR360, 1N5822, SR560). The total filtering capacitors capacity of the rectifier is 20 000  $\mu$ F. The regulator is LM1084 IT-5.0 (position 4 in the fig. 1). The output capacitor is high-quality Elna Cerafine 1000  $\mu$ F 25V.

Second module. It is on the circuit board (position 12 in the fig. 1).

The second module is defined for a supply of the socket P4 (+12 V – power supply of the CPU).

The current consumption of the CPU Intel E7400 in the given cMP2's configuration (the core voltage is no more than 0.9 V, the core speed is 1-1.5 GHz) is no more than 0.5 A. The maximum output current of this module is 2 A. The power transformer is toroidal 75 VA; the voltage of a secondary winding in an idling mode is 12-15 V. The Schottky rectifiers with maximum average forward rectified current 3-5 A (SR350, SR360, 1N5822, SR560). The filtering capacitor capacity of the rectifier is 10 000  $\mu$ F. The regulator is LT1083CP (a position 7 in the fig. 1). The output capacitor is high-quality Elna Cerafine 1000  $\mu$ F 25V.

The adjustment terminal of the LT1083CP is bypassed by the high-grade capacitors Elna Silmic II 10  $\mu$ F 35 V (C5 in the fig.6). It is made in all modules in which the LT1083CP is used.

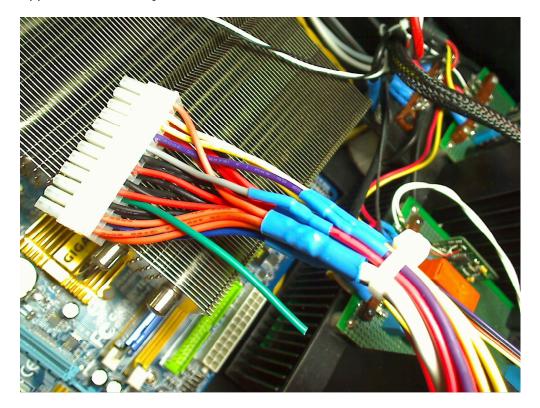

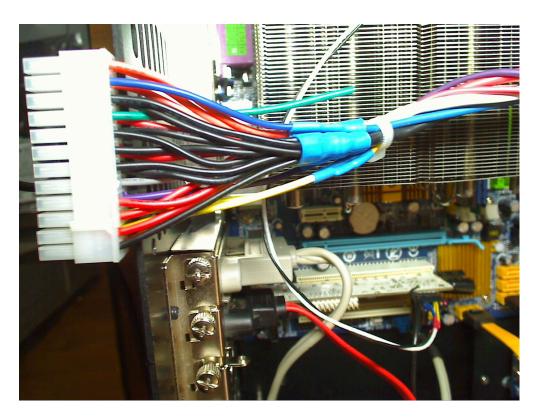

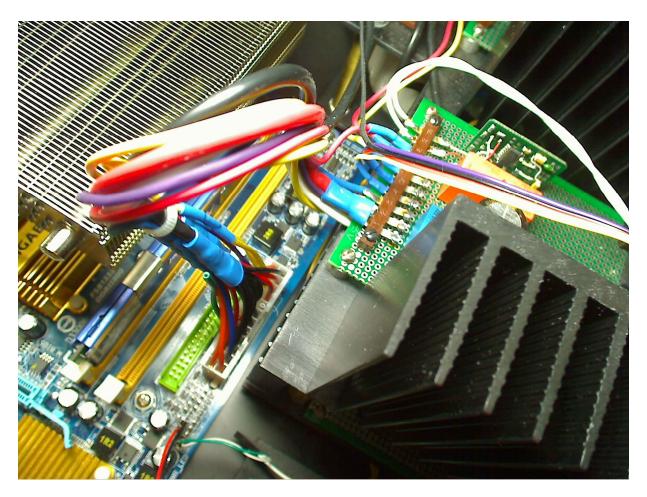

Third module. It is on the circuit boards (position 13 in the fig. 1 and position 10 in the fig. 2).

The third module supplies the system board's socket P24. The voltages are the following: + 3.3 V, + 5 V, + 12 V and - 12 V.

It seems the voltage  $\pm$  5 V is most significant. The real current consumption on the bus  $\pm$  5 V does not exceed 3.5 A. The maximum output current of the third module is 5 A (bus  $\pm$  5 V). The Schottky rectifiers with maximum average forward rectified current 15 A (12TQ045) are installed on the separate heatsink (a position 11 in the fig. 4). The total filtering capacitors capacity of the rectifier is 30 000  $\mu$ F. The circuit design of double consecutive stabilization is applied because of the high significance of a supply  $\pm$  5 V. The first regulator outputs the voltage  $\pm$  6.5 V, and the second regulator outputs the voltage  $\pm$  5 V. Both regulators are LT1083CP (positions 1 and 2 in the fig. 1). The output capacitor is high-quality Elna Cerafine 1000  $\pm$  25V. The circuit design of a 1.5-second delay of supplying voltage to the pin Power Ok ( $\pm$  5 V connector P24) and the circuit design of switching-off of the built-in monitor (a position 3 in the fig. 1) is had . The usage of the linear power module has shown that the voltage  $\pm$  5 V can be supplied to the contact Power Ok simultaneously with other voltages, and switching-off of the built-in monitor does not influence quality of a playback's sound. So these two options it is possible to expel.

The real current consumption on the bus +3.3 V does not exceed 0.3 A. The maximum output current of the third module is 2 A (bus +3.3 V). The Schottky rectifiers with maximum average forward rectified current 3-5 A (SR350, SR360, 1N5822, SR560). The total filtering capacitors capacity of the rectifier is 20 000  $\mu$ F. The regulator is LM1085IT-3.3. It is on the circuit boards (position 10 in the fig.2). The output capacitor is high-quality Elna Cerafine 1000  $\mu$ F 25V.

The real current consumption on the bus +12 V does not exceed 0.15A. The maximum output current of the third module is 3 A (bus +12 V). The Schottky rectifiers with maximum average forward rectified current 5 A (SR560). The filtering capacitor capacity of the rectifier is 10 000  $\mu$ F. The regulator is LM1085IT-12. It is on the circuit boards (position 10 in the fig.2). The output capacitor is high-quality Elna Cerafine 1000  $\mu$ F 25V.

The real current consumption on the bus - 12 V is not known. This voltage is used only at computer start. The maximum output current of the third module is 1 A (bus -12 V). The Schottky rectifiers with maximum average forward rectified current 3-5 A (SR350, SR360, 1N5822, SR560). The filtering capacitor capacity of the rectifier is 10 000  $\mu$ F. The regulator is LM7912. It is on the circuit boards (position 10 in the fig.2). The output capacitor is high-quality Elna Cerafine 1000  $\mu$ F 25V.

The power transformer of the third module is toroidal 100 VA. It has four secondary windings. The voltages of secondary windings in an idling mode are 5-6 V (for +3.3 V), 6-8 V (for +5 V), 12-15 V (for +12 V) and 12-15 V (for -12 V).

Fourth module. It is on the circuit board (position 12 in the fig. 1).

The fourth (service) module provides the stabilized voltage + 5 V and + 12 V. The real current consumption on these voltage can be various in different configurations, therefore we specify the maximum values for the given configuration cMP2 (with one HDD 1000 $\Gamma$ B Western Digital Caviar Green): on the bus +5V – 3A, on the bus +12V – 2A. The Schottky rectifiers with maximum average forward rectified current 5-8 A (SR560, 80SQ045). The filtering capacitors capacity of the rectifiers are 10 000  $\mu$ F. The regulator +5V is LM1084 IT–5.0 (position 5 in the fig. 1). The regulator +12V is LT1083CP (position 6 in the fig. 1). The output capacitors are 470  $\mu$ F. The power transformer of the fourth module is toroidal 75 VA. It has two secondary windings. The voltages of secondary windings in an idling mode are 6-8 V (for +5 V) and 12-15 V (for +12 V).

The terminal block (position 9 in the fig.1) is the center of the PSU's «ground star». The ground buses from all three circuit boards (are soldered by a thick wire to filtering capacitors of rectifiers – see the position 8 in the fig.1) converge here and diverge to the power consumers.

## Appendix 1

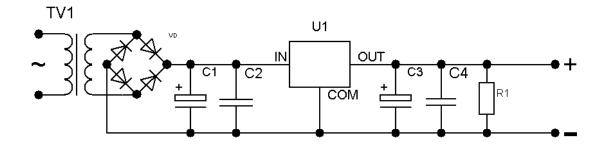

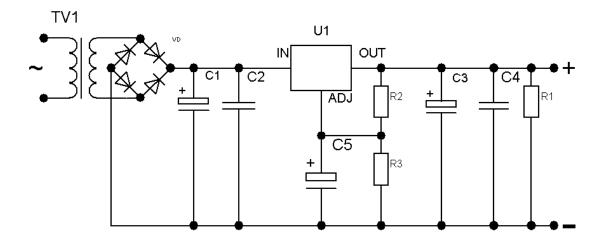

We give the standard schematic of the stabilized power supply unit which it was used for each voltage in the described power supply unit.

Fig.5

Fig.6

The explanatory notes to schematics:

- 1. TV1 the power toroidal transformer

- 2. VD the Schottky rectifiers

- 3. C1 and C2 the filtering capacitors, C3 and C4 output capacitors

- 4. C2 and C4 the qualitative film capacitors with small capacity shunting electrolytic capacitors (the film capacitor capacity is around 1/100 part of the electrolytic capacitor capacity). C2 and C4 are possible not to install in case of use of electrolytic capacitors Black Gate, Elna Cerafine, Elna Silmic, Panasonic FC and similar.

- 5. R1 the load resistor providing the minimum load current (5-10 mA) in the psu's output.

- 6. U1 the regulator: the regulator providing fixed value of stabilized voltage in output of the unit without the additional resistors is represented in the fig.5 and with the additional resistors R2 and R3 is represented in the fig.6. The benefit of the circuit design in the fig.6 is in the additional capacitor C5 providing additional ripple rejection. R2, R3, C5 are chosen according to the regulator's datasheets.

Appendix 2. The external power supply for a digital part of sound card Esi@Juli.

The digital part of sound card Esi@Juli gets a feed from a system board through PCI socket only on the power bus + 5 V.

```

-12V |- B1 A1 -| Test Reset

Test Clock |- B2

A2 -| +12V

Ground |- B3 A3 -| Test Mode Select

Test Data Output |- B4

A4 -| Test Data Input

+5V |- B5 A5 -| +5V

+5V |- B6

A6 -| Interrupt A

Interrupt B |- B7 A7 -| Interrupt C

A8 -| +5V

Interrupt D |- B8

PRSNT1# |- B9

A9 -| Reserved

PRSNT2# |- B11 A11 -| Reserved

:----:

:-----:

Reserved |- B14 A14 -| Reserved

Ground |- B15 A15 -| Reset

Clock |- B16 A16 -| +V I/O

Ground |- B17 A17 -| Grant

Request |- B18 A18 -| Ground

+V I/O |- B19 A19 -| Reserved

Address 31 |- B20 A20 -| Address 30

Address 29 |- B21 A21 -| +3.3V

Ground |- B22 A22 -| Address 28

Address 27 |- B23 A23 -| Address 26

Address 25 |- B24 A24 -| Ground

+3.3V |- B25 A25 -| Address 24

C/BE 3 |- B26 A26 -| Init Device Select

Address 23 |- B27 A27 -| +3.3V

Ground |- B28 A28 -| Address 22

Address 21 |- B29 A29 -| Address 20

Address 19 |- B30 A30 -| Ground

+3.3V |- B31 A31 -| Address 18

Address 17 |- B32 | A32 -| Address 16

C/BE 2 |- B33 A33 -| +3.3V

Ground |- B34 A34 -| Cycle Frame

Initiator Ready |- B35 A35 -| Ground

+3.3V |- B36 A36 -| Target Ready

Device Select |- B37 A37 -| Ground

Ground |- B38 A38 -| Stop

Lock |- B39 A39 -| +3.3V

Parity Error |- B40 A40 -| Snoop Done

+3.3V |- B41 A41 -| Snoop Backoff

System Error |- B42 A42 -| Ground

+3.3V |- B43 A43 -| PAR

C/BE 1 |- B44 A44 -| Address 15

Address 14 |- B45 A45 -| +3.3V

M66EN/Ground |- B46 A46 -| Address 13

Address 12 |- B47 A47 -| Address 11

Address 10 |- B48 A48 -| Ground

Ground |- B49 A49 -| Address 9

Address 7 |- B53 A53 -| +3.3V

+3.3V |- B54 A54 -| Address 6

Address 5 |- B55 A55 -| Address 4

Ground |- B57 A57 -| Address 2

Address 1 |- B58 A58 -| Address 0

+5 I/O |- B59 A59 -| +V I/O

Acknowledge 64-bit |- B60 A60 -| Request 64-bit

+5V |- B61 A61 -| +5V

🔪+5V |- B62 A62 -| +5V 🔫

```

Fig.7

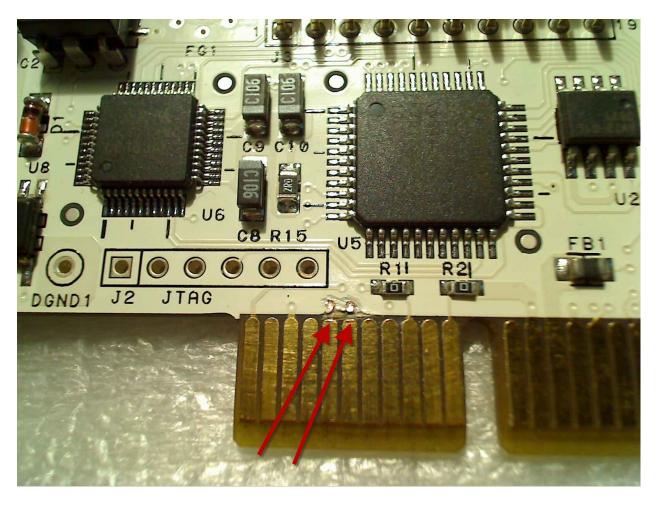

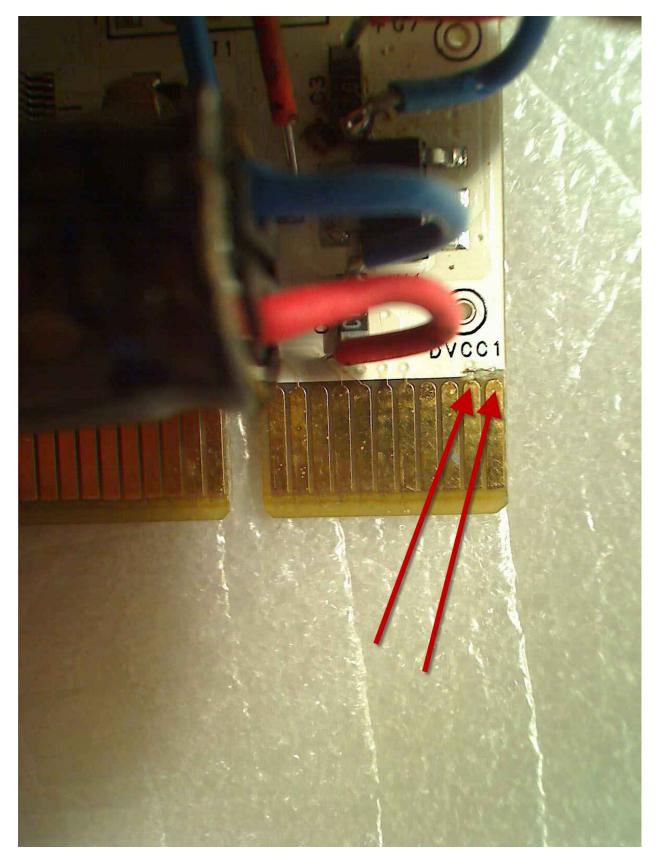

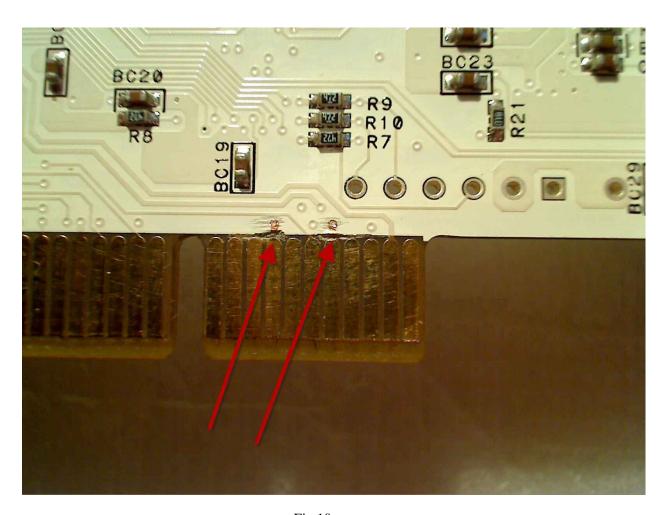

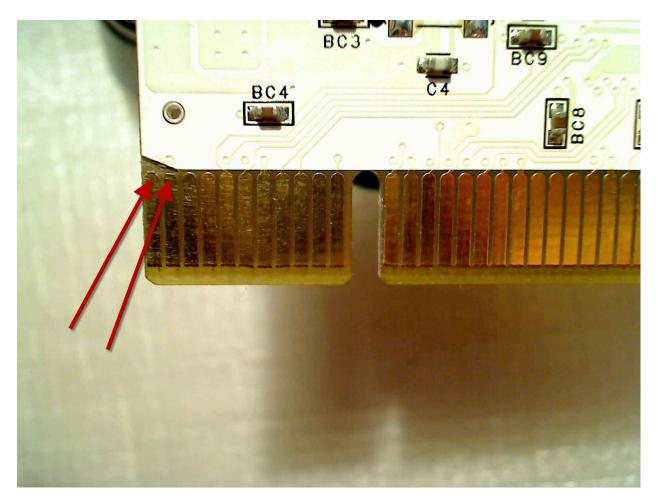

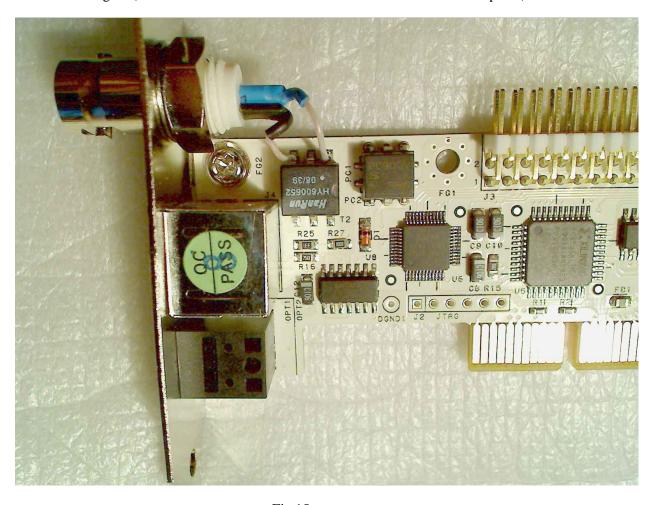

The matching printed conductors on the Juli's board (only 8 conductors) is necessary to cut carefully, as is shown in the fig. 8,9,10,11.

Fig.8

Fig.9

Fig.10

Fig.11

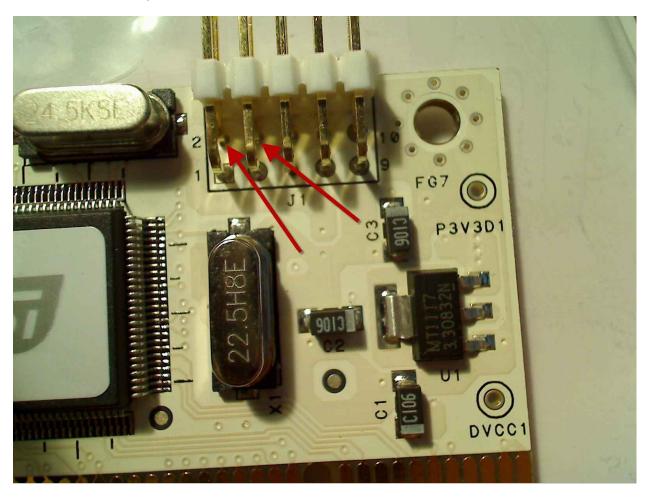

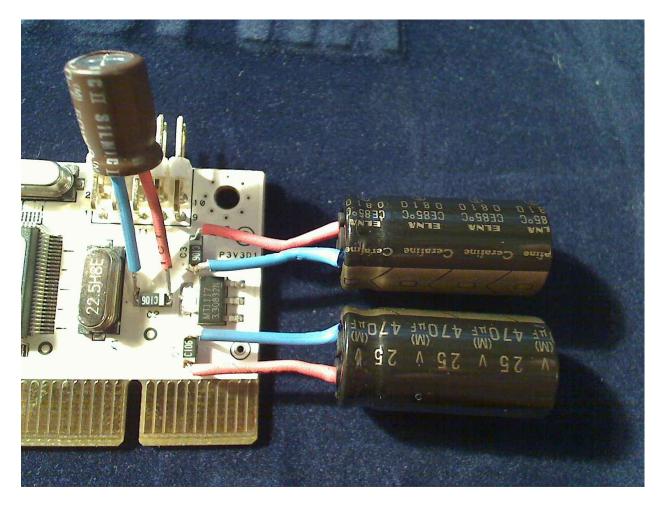

It is convenient to input external voltage + 5 V to the pins 2 (+ 5 V) and 4 ("ground") of the sound card's connector J1 (fig. 12 and 13).

Fig.12

Fig.13

The chip U1 of the voltage regulator + 3.3 V for a power supply of the chip Tremor is visible in the fig. 12. The capacitors C1 and C3 are the input capacitors, C2 is the output capacitor. These capacitors it is recommended bypass by high-grade electrolytic capacitors Elna Cerafine or Elna Silmic 470-1000  $\mu$ F.

Fig.14

It is recommended to install connector BNC (spdif out) on the Juli's backplane, which leading-outs to solder by short conductors directly to leading-outs of the secondary winding of pulse transformer T2, as is shown in the fig.15 (the case of connector BNC should be isolated from the backplane).

Fig.15

Appendix 3. The pinout of the connector P24.

Fig.16

Fig.17

Fig.18

Connector P24: pins 1,2,12,13: +3.3 V; pins 4,6,8,9,21,22,23: +5 V; pin 10,11: +12 V; pin 14: -12V; pins 3,5,7,15,17,18,19,24: ground, pins 16,20: no connection.